# CENTRAL ASIAN JOURNAL OF MATHEMATICAL THEORY AND COMPUTER SCIENCES

https://cajmtcs.centralasianstudies.org/index.php/CAJMTCS Volume: 06 Issue: 03 | July 2025 ISSN: 2660-5309

Article

# Applicability and Assessment of Diverse FPGA Architectures and Algorithms for the Internet of Things Applications

Anitha Velu\*1, Raghu Ramamoorth2

- 1. Assistant Professor, Department of Electronics and Communication Engineering, Sri Sairam College of Engineering, Bengaluru, Karnataka, India

- Assistant Professor, Department of Computer Science and Engineering, The Oxford College of Engineering, Bengaluru, Karnataka, India

- \* Correspondence: aniveluece@gmail.com

Abstract: The "Web of things" (IoT) is turning into an interesting issue in the work environment and outside. IoT is an idea that possibly influences the way of human's life and work area. The IoT can coordinate the actual humankind straightforwardly into PC based frameworks. It additionally permits objects to be detected or controlled from a distance across the current organization framework. IoT further develops proficiency, precision, and monetary advantage of the habit framework to diminish human creation. The test of planning the design in IoT applications is to contract with a copious amount of finding the information produced from the connected appliances that are limited to resources and likely to misplaced information due to the distress in network connectivity. Applications of IoT in the FPGA (Field Programmable Gate Array) framework definitely said to be a challenging one to reach diversity in the upcoming years with the local area networks. FPGA configuration enables a sturdy, less cost architecture that are easy to understand supporting the way of 24 hours of frequent checking with remote detection framework. This paper proposes a review of carrying out the FPGA innovation for IoT applications by investigating different designs. The main aim of this review work is to facilitate the way in which the users can make understand the FPGA-oriented design and architectures embedded with IoT for variety of applications.

**Keywords:** Internet of Things (IoT), Field Programmable Gate Array (FPGA), Network Infrastructure, Smart Devices, Remote Sensing Systems, Real-Time Monitoring

Citation: Velu, A., Ramamoorth, R. Applicability and Assessment of Diverse FPGA Architectures and Algorithms for the Internet of Things Applications. Central Asian Journal of Mathematical Theory and Computer Sciences 2025, 6(3), 534-545.

Received: 30<sup>th</sup> April 2025 Revised: 12<sup>th</sup> May 2025 Accepted: 19<sup>th</sup> May 2025 Published: 26<sup>th</sup> May 2025

Copyright: © 2025 by the authors. Submitted for open access publication under the terms and conditions of the Creative Commons Attribution (CC BY) license

(https://creativecommons.org/lice nses/by/4.0/)

#### 1. Introduction

## Basics of Web of Things (IoT)

The Web of Things or Internet of Things is an arrangement of linked actual objects or gadgets available via the Internet. The term 'thing' in IoT might refer to any individual with a basic monitor or a vehicle that are assembled with sensors, i.e., gadgets that are assigned with an Internet Protocol (IP) address that can assemble and share the information over an organization without any manual intervension or mediation. The implanted technology inside these gadgets/objects assists them by communicating with interior states or the outside climate, which influences the choices taken. IoT interfaces several devices inserted to the fundamental server web. Whenever gadgets/articles can address themselves carefully, they can be controlled anyplace by anyone, as introduced in Figure 1. This network further helps us with gathering additional information from

additional spots, guaranteeing numerous ways of improving effectiveness and further develop safety and security.

**Figure 1.** Concept of Internet of Things (IoT).

IoT can be referred as a groundbreaking energy that could assist the segment with working on its presentation throughout the IoT investigation and security to convey improved outcomes. Some application regions are organizations in the utilities, oil and gas, protection, production, transportation, framework, and retail areas. Each one of these can work on the advantages of IoT by assembling it with greater knowledgeable choices, with the progression of interactivity and value-based data as a supporting factor. This new availability strategy goes past workstations and advanced mobile phones towards connected cars, smart homes, associated wearables, shrewd urban communities, and associated healthcare [1], [2]. Which can be mentioned by the term connected life. As per the Gartner statement, illustrated in Table 1, near to the year 2025, the associated gadgets across the innovations might arrive at 20.6 billion. VLSI technology plays a vital role in development of Internet of things (IoT) for a wide range of applications like agriculture, industrial automation, smart cities, health care, traffic control and so on [3],[4],[5],[6], [7].

**Table 1.** Approximate number of devices connected (present and in future).

| Year | Number of connected devices |  |  |

|------|-----------------------------|--|--|

| 1989 | 0.28 million                |  |  |

| 1998 | 89.0 million                |  |  |

| 2012 | 6.0 billion                 |  |  |

| 2014 | 10.0 billion                |  |  |

| 2025 | 1.02 trillion               |  |  |

|      |                             |  |  |

### System architecture of IoT applications

Internet of Things is worldwide milieus in which the regular gadgets turn out to be more smart, handling of devices grow to be savvy, and transmission gets more instructive. A short review of P.P.Ray portrays the IoT-established system designs as competent and

efficient to work on the comprehension of connected tools, innovation, and strategy to work with the designer's prerequisite [8]. The review depicts the latest things in engineering to inspire educational and production purposes to engage in the specific influence of IoT.

Design of IoT framework incorporates four phases, in particular:

- Stage 1: comprises of organized things, for instance remote sensors and actuators.

- Stage 2: incorporates the major details like sensor information, aggregation systems, and analog-to-digital conversions.

- Stage 3: tends to limit the IT frameworks to execute the information pre-processing prior to moving to the data to the server farm or the cloud.

- Stage 4: then the processed information is analyzed, managed, and stored on conservative client-facing server farm structures.

#### **Problem Statement**

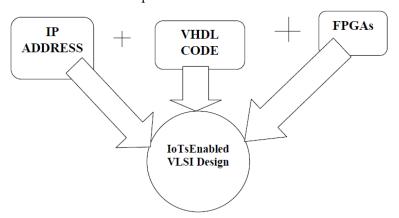

Internet of Things (IoT) will comprise of billions of gadgets in no time. There have been expectations that, continuously 2020, around 8 billion gadgets will have connectivity to the Internet. This technology's deployment will require changes to the ongoing organization framework, protocols and services. It can likewise be conveyed by empowering the VLSI [9], [10] plan or a VHDL code; the precise representation is implied, as displayed in Figure 2. The making of compound applications that are important for various enterprises can be worked with utilizing IoT [11],[12]. These applications will be the part of everyday life existence, and their effect on our general public is critical. The assumptions for income amazing open doors are around \$ 2.7 trillion. Many issues, for example, no standardized architecture, security, safety concerns, and interoperability between merchants, plague IoT. Henceforth, our work is to execute the innovation worldview for IoT on FPGA. Utilizing FPGA models gives improved results in light of its benefits like minimal expense, less chance to advertise, re-programmability, and lesser area utilization of about 28nm CMOS plan innovation.

Figure 2. VLSI design by enabled with IoT.

#### **Role of FPGA in IoT Applications**

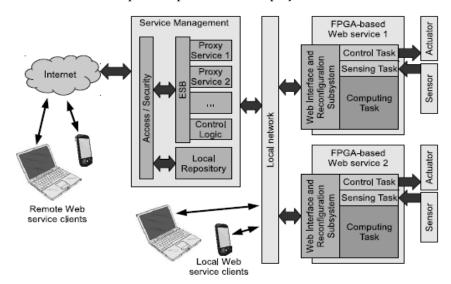

FPGA based devices are predictable to take over the IoT based environment in next few years. The connected gadgets can undoubtedly communicate with rest of the world to enjoy the benefit of giving the most reduced power, least latency, and best acceptance rate. Sensors with IoT features can be connected to measure temperature and humidity, current and voltage, vehicle or automobile acceleration, location, force, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and other assorted purposes [13]. The overall idea of re-organization of FPGA-based web administration is exemplified in Figure 3.

FPGA is integrated with Acron RISC Machine (ARM) processors [14], [15], [16] to utilize the most essential programming capabilities like web servers or protection packages assuming that a more elevated level of handling is required. The significant idea in developing is the programmable element of an FPGA platform. A developer advancement kit is expected to configure FPGA in fostering the IoT environment cycle. All the while, as required, a Printed Circuit Board (PCB) is designed including explicit sensor/correspondence/ and some output components like displays.

Figure 3. Reconfigurable FPGA-based web service.

#### Disputes and design concern

The disputes in IoT design incorporates protection, unapproved access, unauthorized organizations, and contradiction of administration. Developer should overcome huge execution difficulties to arrive at billions or trillions of connected gadgets to form the IoT cloud. Handling huge data generated by various sensors is difficult for any VLSI system to deploy update technologies, in order to handle that ontology based data compression has been produced by various research works [17], [18], [19], [20], [21], [22]. Among them, a portion of the keys will make IoT gadgets power-proficient, dealing with incompatible connection points, and providing a processing development way to deal with the inevitable expansion in performance requirements of the connected appliances. A FPGA-oriented system design can assist with solving the above mentioned discrepancies.

# 2. Materials and Methods

A basic least-intricacy FPGA accomplishment of multi-spectral and Hyper-spectral Lossless Compressor (HyLoC) for some applications in space has been introduced by Santos et al. [23]. In current and future space missions, effective compression of hyper-spectral pictures locally available satellites is obligatory to save data transfer capacity and least storage area. Lessening the volume of information in space is identified to be a major challenge faced in two-phased methodology [24], [25]. This work aims to propose a novel, higher productive compression calculations and produce innovations and make the systems to perform the compression in locally accessible equipment.

Hardware architecture is considered and intended to accomplish a least hardware inhabitance and greater execution on a space-qualified application of FPGA system from the miniature unit. This uses the Consultative Committee for Space Data Systems (CCSDS123) calculation is illustrated in the stream chart in Figure 4. The subsequent FPGA execution is, in this way, reasonable for installed compression. The proposed execution

benefits are additionally confirmed by a demonstrator carried out on a viable prototype (i.e., PCB board) through Xilinx tool. In conclusion, an examination among other FPGA kits are executed using locally available data compression approaches were presented [26], [27], [28].

Figure 4. Stream chart of CCSDS123 algorithm.

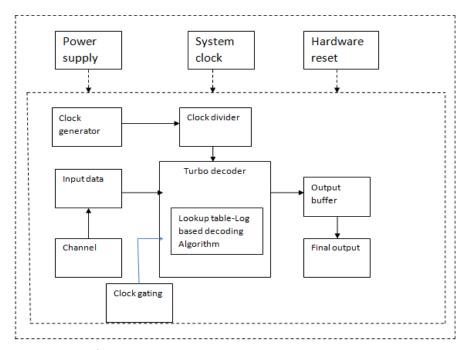

Anitha et al. [29], [30], [31] have established Very Large Scale Integration (VLSI) based system design with a clock-gated turbo encoder for wireless sensor networks [32], [33] . This work is carried out through establishing a clock gating strategy to decrease power utilization, as illustrated in Figure 5. This architecture utilizes an essential Add Compare Select (ACS) activity. Parallel processing activity of ACS blocks leads to low handling steps that consequently leading to a least transmission energy with lesser design complexity as well. This research work execution implements a high throughput, less memory prerequisite, diminished complexity, and decreased power utilization.

Velu et al. [31] have proposed an Orthogonal Frequency-Division Multiple Access (OFDMA) way of encoding and decoding method for Network Operations Center (NOC) in Multi-Input and Multiple-Output (MIMO) architecture to improve the speed and efficiency of communication. The proposed calculation is an interesting strategy for the stage to sine sufficiency transformation, which gives quick and region effective calculations of mathematical functions namely sine and cosine. The developed CORDIC implementation involves pipeline processing to support the proceeded data path. Through utilizing pipeline engineering, the proposed design can compute consistent input results in higher throughput which needn't bother with memory or temporary registers in order to save the angle iteration.

Figure 5. Clock-gating turbo decoder architecture.

The Fiber-Wireless Sensor Networks (Fi-WSNs) that are made out of a fusion Fiber-Wireless (FiWi) networks improved with sensors will assume a critical part in sustaining the Machine-to-Machine (M2M) correspondences. This combination helps to empower a wide scope of Internet of Things (IoT) appliances, through which the smart frameworks address a significant real-world model.

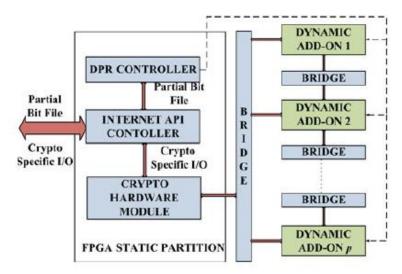

Chances of designing an energy-proficient Fi-WSN in view of Ethernet Passive Optical Network (EPON)/10G-EPON, Wireless Local Area Network (WLAN), remote sensors, and aloof fiber based optic sensors are insisting. The implementation is considered as common interchanges foundation for wider bandwidth administrations and smart equipments that has been investigated by Van et al. [34]. The Internet of Things (IoT) is a dynamic, ever developing "living" element. Henceforth, in present days the FPGA-oriented smart gadgets embedded with Dynamic Partial Reconfiguration (DPR) abilities, permits in-field harmless changes for the electronic circuit executed on the FPGA [37]. Typically, the enactment of proposed DPR abilities involves extra licenses from the FPGA merchant, as illustrated in Figure 6.

Figure 6. The architecture of proposed FPGA system with enabled-DPR.

The customized DPR [35] [36], [38], [39] approach doesn't need any additional "add-on" implementation to carry out a insubstantial cryptographic protection protocols. The proposed work depicts the benefit of the DPR capacities in FPGA over the IoT applications. This additionally investigates the potential dangers that could appear due to DPR accessibility on the IoT nodes. This work also includes a few potential arrangements in view of Physically Unclonable Function (PUF) electronic circuits to forestall such dangers. Cognitive radios (CR) empower productive range used for evaluating range detecting to figure out current range inhabitance and progressively reconfiguring the correspondence boundaries, making them profoundly appropriate for IoT frameworks.

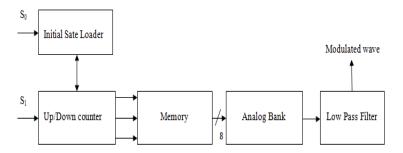

**Figure 7.** The architecture of low complex QPSK modulator.

Kiran et al. [40] proposes a QPSK-based transmitter architecture with a low complex circuit design avoiding the mixer component, as illustrated in Figure 7. A prototype model is created in this work utilizing FPGA as the baseband regulator and Bipolar Junction Transistors (BJTs) as a main component. This developed architecture handily adjusted to MOSFET innovation, whereas the regulation has been accomplished exclusive of producing the transporter remotely. This prototype model was effectively experimented by producing input frequencies of reach shifting from 1 kHz - to 120 MHz. This methodology can likewise be utilized for some other advanced regulation plan, for example, Frequency Shift Key (FSK), Binary Phase Shift Key (BPSK), and so on.

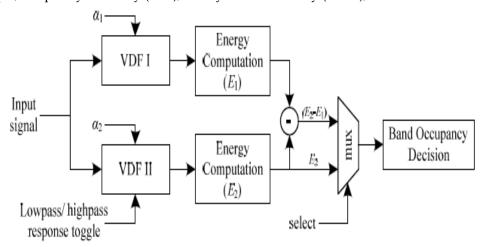

**Figure 8.** Block diagram of the VDF-based spectrum sensing scheme.

Ambede et al. [41] has developed Variable Digital Filter (VDF) oriented equipment executed with a range detecting plan for CR (Cognitive Radio) grounded IoT framework applications which involves huge transmission capacity. This developed prototype model is evaluated on FPGA, as illustrated in Figure 8. In general the proposed prototype accomplishes superior execution with less resource consumption and at partially greater power utilization [42], [43].

In the proposed scheme, two VDFs giving unedited command above the cutoff recurrence were utilized to figure power requirement in comparison with all the three frequency bandwidth cases. The productive experimentation utilizes the range detecting plan and gives equipment execution models to the VFDs on various FPGA kits with different functionalities [44], [45], [46], [47], [48], [49], [50]. FPGAs are ultimate contender for Cognitive Radios. FPGAs permit compound calculations to increase the processing speed of an equipment and deal methods to powerfully adjust equipment units and helps multi-standard cognitive radio or proficient molding/range detecting procedures.

#### 3. Results and Discussion

The proposed methodology for designing FPGA architecture for IoT applications heads toward the goals like designing and developing an FPGA-embedded IoT execution for multi-layered sensor nodes and control systems. They are using low-cost FPGA to implement the overall IoT subset, as well as control systems, data acquisition, etc. Manifestation of a simple FPGA kit containing and controlling a number of IOT implementations simultaneously is considered. The proposed design develops a high-level VHDL program in order to make possible to the multi-platform portability for IoT based implementations.

This paper reviews the current FPGA architectures and algorithms developed for the IoT domain till the year 2020. This manuscript identifies various proposed new architectures' design principles and advantages from other architectures' shortcomings. Various design issues in the FPGA platform for IoT applications, such as security issues, performance and interoperability have been addressed in this manuscript. The comparison study of few essential parameters and characteristics of the proposed FPGA architectures are illustrated in Table 2.

FPGAs are used to bridge the gap between software and hardware by offering a number of advantages like:

- a. Low cost

- b. Flexibility

- c. Fast time-to-market

- d. Long-term maintenance and

- e. Reliability.

Keeping in account of all the approaches and architectures discussed above for review, it can be accomplished that the FPGA is a best reconfigurable system hardware for implementing IoT based applications. By comparing various algorithms from Table II, it can be concluded that when less storage is recommended, clock-gating BCJR of about 128.8kb, CCSDS123, and DPR-based approach is about 150kb is said to be efficient. While designing the FPGA architecture for IoT, if the cost is considered, then CORDIC and DPR approaches will give better results at the same time for high-frequency operations; the Nb-IoT-based FPGA design is said to be more efficient since its operating frequency ranges from 750MHz to 960MHz. The Eco-SFiWi-based design is said to have less power consumption of about 120mW; similarly, algorithms like CCSDS123, DPR, and CORDIC algorithm also support low power consumption IoT applications. CCSDS123 algorithm and the clock-gating BCJR algorithms have less design complexity FPGA of about 74% and 71%, respectively.

**Table 2**. Comparative analysis of various FPGA architectures proposed for IoT applications.

| -        |                                    | Parameters Measured |                   |                     |              |                             |  |

|----------|------------------------------------|---------------------|-------------------|---------------------|--------------|-----------------------------|--|

| S.<br>No | Name of the architecture/ approach | Complexity          | Power consumption | Operating frequency | Cost         | Storage/<br>memory<br>space |  |

| 1        | CCSDS123                           | Low                 | High              | -                   | H/W cost is  | Lesser                      |  |

|          | [17]                               |                     | (>400mW)          |                     | high         |                             |  |

| 2        | CORDIC                             | Medium              | Reduced           | 199.28MHz           | Less         | No need                     |  |

|          | [19]                               | 74%                 |                   |                     |              | for                         |  |

|          |                                    |                     |                   |                     |              | external                    |  |

|          |                                    |                     |                   |                     |              | memory                      |  |

| 3        | Clockgating<br>BCJR [18]           | Less 71%            | Reduced by 32%    | 120MHz              | -            | 128.8kb                     |  |

| 4        | DPR [24]                           | -                   | Low               | 180MHz              | Low          | 150kb                       |  |

|          |                                    |                     |                   |                     | maintenance  |                             |  |

|          |                                    |                     |                   |                     | cost         |                             |  |

| 5        | Eco-SFiWi<br>[23]                  | High 86%            | Low (120mW)       | -                   | Less         | 320kb                       |  |

| 6        | QPSK based                         | Medium              | Less              | 1KHz-               | Low          | _                           |  |

| Ü        | [26]                               | 76%                 | 200               | 120MHz              | 2011         |                             |  |

| 7        | VDF [29]                           | Medium              | High (269mW)      | 100MHz              | High         | Large                       |  |

|          | . [ . ]                            | 76%                 | 8 ( 3 7 7)        |                     | implementati | memory                      |  |

|          |                                    |                     |                   |                     | on cost      | capacity                    |  |

| 8        | NB-IoT                             | High 84%            | Very low          | 750-                | High         | low                         |  |

|          | based [14]                         | O                   | J                 | 960MHz              | maintenance  |                             |  |

|          | . 1                                |                     |                   |                     | cost         |                             |  |

It can be understood that algorithms such as CORDIC, CCSDS123, and DPR-based approaches are more efficient, with low complexity of about 71%, lesser power consumption of about 120mW, and can be operated at a high-frequency rate ranges about 750MHz-960MHz when compared to the convolution algorithms.

#### 4. Conclusion

Implementing FPGA architecture on the IoT platform is a more efficient and userfriendly approach for real-time applications. The expertises in core infrastructure layers in day-to-day world were showing good signs of development. In future work, we consider the BCJR approach because of its low complexity of about 71% and less storage space of about 128.8kb, and reduced power consumption by 32% along with Nb-IoT based approach due to its high operating frequency of about 750MHz-960MHz and CORDIC architecture because of its reduced power consumption, less cost, 74% complexity and operating frequency of about 199.28MHz. Considering all the above advantages, a new FPGA approach will be designed for IoT applications. IoT has been finished up as the normal eventual future of Network/Internet. IoT associates billions and trillions of gadgets and empowers M2M correspondence. This could change day to day existence with ordinary objects associated to the Internet connectivity. As of now, this field is in an exceptionally nacent stage. In any case, significantly an added requirement has to arise in IoT based applications and correspondence technologies. These fields tends to develop and influence human existence in incomprehensible ways over the course of the following 10 years.

#### REFERENCES

- [1] J. Lin, W. Yu, N. Zhang, X. Yang, H. Zhang, and W. Zhao, "A survey on internet of things: Architecture, enabling technologies, security and privacy, and applications," *IEEE Internet of Things Journal*, vol. 4, no. 5, pp. 1125–1142, 2017.

- [2] R. Ramamoorthy and M. Thangavelu, "An enhanced hybrid ant colony optimization routing protocol for vehicular ad-hoc networks," *Journal of Ambient Intelligence and Humanized Computing*, vol. 13, no. 8, pp. 3837–3868, 2022.

- [3] R. Ramamoorthy and M. Thangavelu, "An improved distance-based ant colony optimization routing for vehicular ad hoc networks," *International Journal of Communication Systems*, vol. 33, no. 14, e4502, 2020.

- [4] A. Velu, R. Ramamoorthy, S. Kumar, and K. Shruthi, "IoT enabled smart farming: a controlled environment agriculture application," in *Proc. Int. Conf. Sustainable Communication Networks and Application (ICSCNA)*, pp. 292–298, Nov. 2023.

- [5] V. Anitha and T. Menakadevi, "A survey paper on implementation of VLSI architecture for internet of things applications," in *Proc. 32nd Indian Engineering Congress*, Chennai, pp. 189–195, 2017.

- [6] A. Velu, "An efficient method for segmentation of cerebrospinal fluid in hydrocephalus affected T2 weighted MRI images," *Central Asian Journal of Theoretical and Applied Sciences*, vol. 3, no. 5, pp. 493–511, May 2022.

- [7] R. Ramamoorthy and M. Thangavelu, "An enhanced distance and residual energy-based congestion aware ant colony optimization routing for vehicular ad hoc networks," *International Journal of Communication Systems*, vol. 35, no. 11, e5179, 2022.

- [8] P. P. Ray, "A survey on Internet of Things architectures," *Journal of King Saud University-Computer and Information Science*, pp. 6–20, Oct. 2016.

- [9] M. Ashwin, R. C. A. Naidu, R. Ramamoorthy, and E. S. Kumar, "IoT-based smart wearable devices using very large scale integration (VLSI) technology," in *Int. Conf. Soft Computing and Signal Processing*, pp. 155– 164, Jun. 2023.

- [10] R. Ramamoorthy, S. M. Manasa, and A. Velu, "Priority based lightweight cluster routing for efficient communication in vehicular ad hoc networks," *Central Asian Journal of Mathematical Theory and Computer Sciences*, vol. 5, no. 2, pp. 52–63, 2024.

- [11] M. Ashwin, E. S. Kumar, R. C. A. Naidu, and R. Ramamoorthy, "IoT based innovative teaching learning using smart class rooms," in *Proc. Int. Conf. Sustainable Computing and Data Communication Systems* (ICSCDS), pp. 1143–1148, Mar. 2023.

- [12] R. Ramamoorthy, "An enhanced location-aided ant colony routing for secure communication in vehicular ad hoc networks," *Human-Centric Intelligent Systems*, vol. 4, no. 1, pp. 25–52, 2024.

- [13] K. K. Sharma, V. Gopi Raju, and V. Gopi Varma, "A review of FPGA implementation of Internet Of Things," *International Journal of Scientific & Engineering Research*, vol. 8, no. 4, pp. 16203–16207, Apr. 2017.

- [14] Z. Song, X. Liu, X. Zhao, Q. Liu, Z. Jin, and B. Chi, "A low-power NB-IoT transceiver with digital-polar transmitter in 180-nm CMOS," *IEEE Transactions on Circuits and Systems*, pp. 610–623, Feb. 2017.

- [15] R. Ramamoorthy and M. Thangavelu, "An enhanced bio-inspired routing algorithm for vehicular ad hoc networks," *Trends in Sciences*, vol. 19, no. 10, p. 4188, 2022.

- [16] R. Ramamoorthy and M. Thangavelu, "Group based dual mode key management scheme for secure communication in vehicular ad hoc networks," Wireless Personal Communications, vol. 120, no. 2, pp. 949– 973, 2021.

- [17] A. Velu and M. Thangavelu, "Ontology based ocean knowledge representation for semantic information retrieval," *Computers, Materials & Continua*, vol. 70, no. 3, 2022.

- [18] A. Velu and M. Thangavelu, "Ocean knowledge representation through integration of big data employing semantic web technologies," *Earth Science Informatics*, vol. 15, no. 3, pp. 1563–1585, 2022.

- [19] A. Velu and M. Thangavelu, "Hetero-GCD2RDF: An interoperable solution for geospatial climatic data by deploying semantic web technologies," *Wireless Personal Communications*, vol. 117, no. 4, pp. 3527–3551, 2021.

- [20] R. Raghu, R. Prabhushankar, J. Rajaram, and M. Vaiyapuri, "Efficient dead reckoning approach for localization prediction in VANETs," *J. Appl. Sci. Comput.*, vol. 6, no. 3, pp. 2093–2099, 2019.

- [21] R. Raghu and T. Menakadevi, "A survey on anonymous secure on-demand routing protocols in MANETs," *Middle East Journal of Scientific Research*, vol. 24, pp. 3869–3880, 2016.

- [22] A. Velu and M. Thangavelu, "Information retrieval through a knowledge base system: Semantic web based approach in South-Eastern Coastal areas of India," *Songklanakarin Journal of Science & Technology*, vol. 44, no. 1, 2022.

- [23] L. Santos et al., "Multispectral and hyperspectral lossless compressor for space applications (HyLoC): A low-complexity FPGA implementation of the CCSDS 123 standard," *IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing*, vol. 9, no. 2, pp. 757–770, 2015.

- [24] V. Anitha and T. Menakadevi, "VLSI architecture of a clock-gating turbo encoder for wireless sensor network applications," *IJISET International Journal of Innovative Science, Engineering & Technology*, vol. 2, no. 12, pp. 577–585, Dec. 2015.

- [25] R. Ramamoorthy et al., "Reliable and accurate plant leaf disease detection with treatment suggestions using enhanced deep learning techniques," *SN Computer Science*, vol. 4, no. 2, p. 158, 2023.

- [26] V. Anitha and T. Menakadevi, "VLSI implementation of a parallel turbo-decoder for wireless communication," *International Journal of Innovative Research in Science, Engineering & Technology*, vol. 5, Special Issue 2, pp. 104–108, Mar. 2016.

- [27] D. Smitha, R. A. G. H. U. Ramamoorthy, and D. R. C. A. Naidu, "OHAR: optimized human action recognition paradigm using optimized type-2 neuro-fuzzy classifier," *Periodico Tche Quimica*, vol. 91, no. 4, pp. 684–699, 2021.

- [28] R. Raghu, M. Hema, and J. J. Priya, "Efficient cluster based algorithm for structured wireless sensor networks," *CIKITUSI Journal for Multidisciplinary Research*, vol. 6, pp. 282–288, 2019.

- [29] V. Anitha and T. Menakadevi, "An efficient VLSI architecture of a clock-gating turbo decoder for wireless sensor network applications," *International Journal of Engineering Research & Science*, vol. 2, no. 3, pp. 25–40, Mar. 2016.

- [30] V. Anitha and T. Menakadevi, "A new OFDMA encoding and decoding method for NOC using MIMO," *International Journal for Scientific Research & Development*, vol. 6, no. 1, pp. 336–340, Mar. 2018.

- [31] V. Anitha and T. Menakadevi, "An efficient DMA encoding and decoding scheme using MIMO architecture for wireless network applications," *International Journal of Innovative Research in Science, Engineering and Technology*, vol. 7, Special Issue 1, pp. 44–53, Mar. 2018.

- [32] M. Ashwin, E. S. Kumar, R. C. A. Naidu, and R. Ramamoorthy, "IoT based innovative teaching learning using smart class rooms," in *Proc. Int. Conf. Sustainable Computing and Data Communication Systems* (*ICSCDS*), pp. 1143–1148, Mar. 2023.

- [33] R. Ramamoorthy, S. Kumar, and R. C. A. Naidu, "Hybrid multihop routing mechanism with intelligent transportation system architecture for efficient routing in VANETs," in *Proc. Int. Conf. Disruptive Technologies for Multi-disciplinary Research and Applications (CENTCON)*, vol. 2, pp. 69–74, Dec. 2022.

- [34] D. P. Van, B. P. Rimal, M. Maier, and L. Valcarenghi, "Design, analysis, and hardware emulation of a novel energy conservation scheme for sensor enhanced FiWi networks (ECO-SFiWi)," *IEEE Journal on Selected Areas in Communications*, vol. 34, no. 5, pp. 1645–1662, 2016.

- [35] R. Ramamoorthy, R. C. A. Naidu, and S. Kumar, "Performance investigation of hybrid bio-inspired zone routing protocol over proactive and reactive routing protocols," in *Proc. Int. Conf. Sustainable Communication Networks and Application (ICSCNA)*, pp. 1–6, Nov. 2023.

- [36] K. Shruthi, R. C. A. Naidu, and R. Ramamoorthy, "Movement record-oriented particle swarm optimization for resource allocation and solving job failure problems in cloud," *European Chemical Bulletin*, vol. 12, no. 12, pp. 392–403, 2023.

- [37] A. P. Johnson, R. S. Chakraborty, and D. Mukhopadhyay, "A PUF-enabled secure architecture for FPGA-based IoT applications," *IEEE Transactions on Multi-Scale Computing Systems*, vol. 1, no. 2, pp. 110–122, 2015.

- [38] J. Raghu, A. Jayanatiya, M. Karunya, and M. Meena, "A trust scheme based on event report for communication in VANETs (TSERC)," *Academia.edu*, [Online]. Available: https://www.academia.edu/download/67395826/IJARCCE.2020.9309.pdf.

- [39] R. Raghu, B. Nawaz, S. S. Sundar, and A. S. Kumar, "Enhanced DSR protocol to analyze black hole attack in MANETs using NS2," *Academia.edu*, [Online]. Available: https://www.academia.edu/download/67395762/jeca 2024.35 f.pdf.

- [40] M. S. Kiran, P. Rajalakshmi, and B. Jagadish, "IoT enabled communication device with mixer-less low complex QPSK based transmitter architecture for low frequency applications," in *Proc. Int. Symp. Wireless Personal Multimedia Communications (WPMC)*, pp. 316–321, Sept. 2014.

- [41] A. Ambede, A. P. Vinod, and S. Shreejith, "Efficient FPGA implementation of a variable digital filter based spectrum sensing scheme for cognitive IoT systems," in *Proc. Global Internet of Things Summit* (*GIoTS*), pp. 1–4, Jun. 2017.

- [42] E. S. Kumar et al., "Comparative study and analysis of cloud container technology," in *Proc. Int. Conf. Computing for Sustainable Global Development (INDIACom)*, pp. 1681–1686, Feb. 2024.

- [43] E. Saravana Kumar, P. Ramkumar, H. S. Naveen, R. Ramamoorthy, and R. C. A. Naidu, "Classification of COVID-19 with belief functions and deep neural network," *SN Computer Science*, vol. 4, no. 2, p. 178, 2023.

- [44] V. Anitha and T. Menakadevi, "A knowledge based approach to personify ocean data in RDF format by the exploitation of semantic technology," in *Proc. 33rd Indian Engineering Congress*, Udaipur, pp. 80–84, 2018.

- [45] V. Anitha and T. Menakadevi, "A survey paper on ontology concepts in semantic web technology and it's applications," *International Journal of Innovative Science and Research Technology*, vol. 3, no. 6, pp. 181–185, Jun. 2018.

- [46] R. Ramamoorthy, S. M. Manasa, and J. A. Smitha, "Android app-oriented smart supervision of water distribution using internet of things," in *Int. Conf. Artificial Intelligence and Smart Energy*, pp. 223–237, Mar. 2024.

- [47] S. M. Manasa, R. Ramamoorthy, A. Velu, and S. Chaitrashree, "Deep learning-based age and gender prediction through feature extraction from facial images using convolutional neural networks," in *Proc. Int. Conf. Communication, Computing & Industry 6.0 (C2I6)*, pp. 1–7, Dec. 2024.

- [48] R. Ramamoorthy, A. Velu, R. C. A. Naidu, A. Kumari, and H. Kumar, "Impact of ant colony optimization on optimal routing for vehicular ad hoc networks," in *Proc. Int. Conf. Communication, Computing & Industry 6.0 (C2I6)*, pp. 1–6, Dec. 2024.

- [49] A. Velu, R. Ramamoorthy, and D. Navulkumar, "An energy efficient IoT based smart street lighting using low cost SoC," in *Proc. Int. Conf. Electronics, Computing, Communication and Control Technology (ICECCC)*, pp. 1–6, May 2024.

- [50] S. Balasubramaniam, S. Kadry, A. Prasanth, and R. K. Dhanaraj, Eds., *Generative AI and LLMs: Natural Language Processing and Generative Adversarial Networks*. Berlin, Germany: Walter de Gruyter GmbH & Co KG, 2024.